Parenting Classes For Special Needs Child Near Me It is possible to operate the USCI in SPI slave mode while the device is in LPM4 and all clock sources are disabled The receive or transmit interrupt can wake up the CPU from any low

I m trying to write a MSP430 application that emulates an EEPROM memory by using MSP s flash as the storage backend The MSP must be configured as SPI slave and respond to the Contribute to aviatoreee MSP430 Examples development by creating an account on GitHub

Parenting Classes For Special Needs Child Near Me

Parenting Classes For Special Needs Child Near Me

Parenting Classes For Special Needs Child Near Me

http://pacoimaadc.com/wp-content/uploads/2016/11/IMG_4232-e1478723567117.jpg

MSP430x24x Demo USCI A0 SPI 3 Wire Slave multiple byte RX TX Description SPI master communicates to

Templates are pre-designed files or files that can be used for numerous purposes. They can conserve effort and time by providing a ready-made format and design for creating different sort of content. Templates can be used for individual or professional jobs, such as resumes, invitations, leaflets, newsletters, reports, presentations, and more.

Parenting Classes For Special Needs Child Near Me

25 Best Religious 80th Birthday Wishes Messages Quotes 42 OFF

When Parenting A Child With Special Needs The Need For Self care Is

Bolt On Bits Discovery Hot 300Tdi Headlight

Parent Education STEM Academy

Step Parent Quotes And Poems QuotesGram

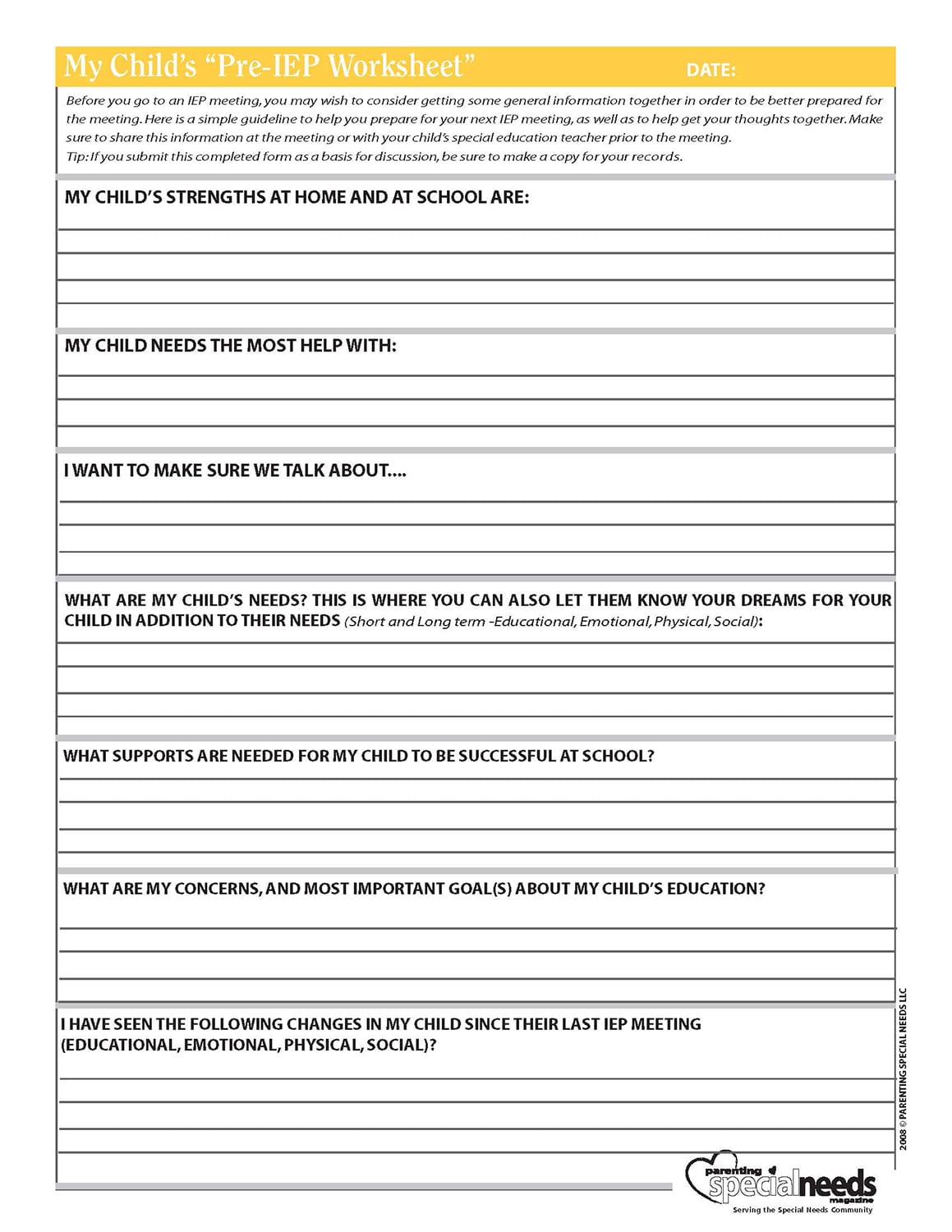

Cultivate Strong Parenting Skills With Engaging Worksheets

https://dev.ti.com › tirex › explore › node

MSP430F522x Demo USCI A0 SPI 3 Wire Slave multiple byte RX TX Description SPI master communicates to

https://e2e.ti.com › ...

I m trying to develop an SPI slave The purpose is the following The MSP430 is a sensor module and comunicate via SPI with an ARM processor SPI master The MSP430 use a GPIO like an

https://amykyta3.github.io › group___m_o_d___s_p_i.html

Jan 8 2013 nbsp 0183 32 This module abstracts out the SPI controller to operate as a master to slave only peripherals

https://argenox.com › library

Apr 12 2025 nbsp 0183 32 SPI is a full duplex protocol in which the slave and the master exchange data at each transition of the clock by setting MOSI and MISO to a bit value Note that MOSI and

https://software-dl.ti.com › ... › html › group__usci__b__spi__api.html

Enables the indicated SPI interrupt sources Only the sources that are enabled can be reflected to the processor interrupt disabled sources have no effect on the processor

[desc-11] [desc-12]

[desc-13]