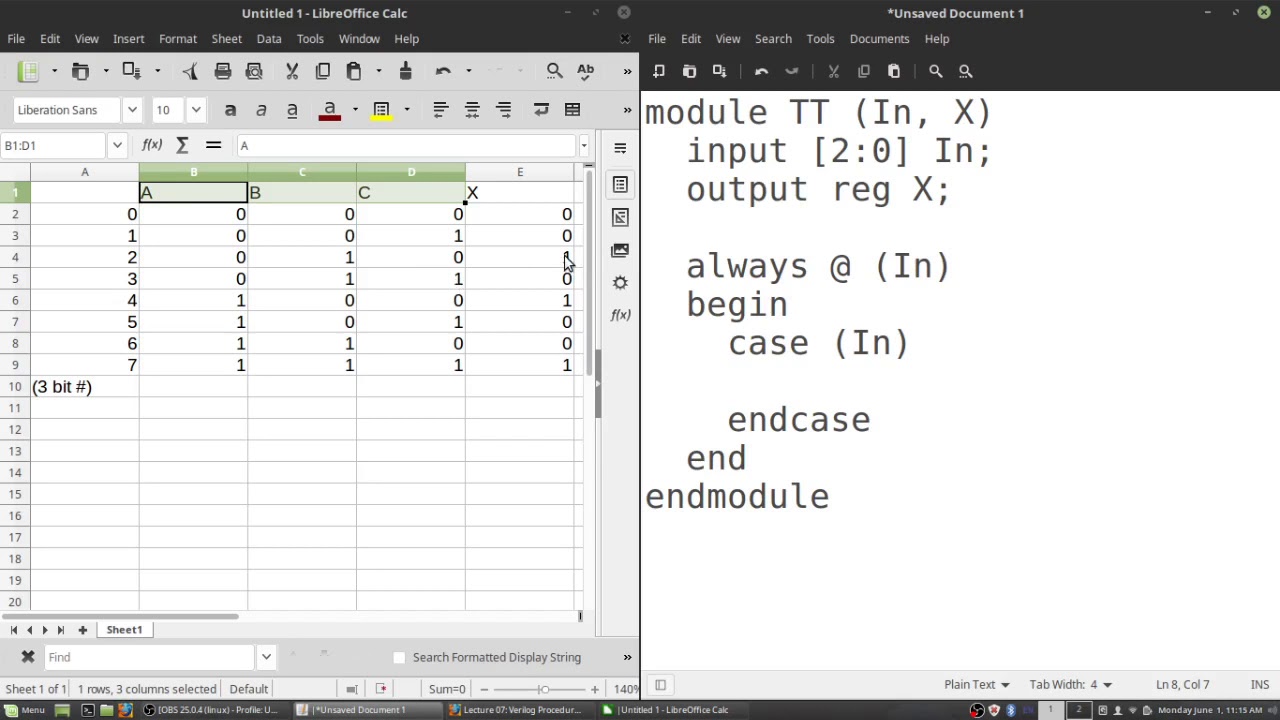

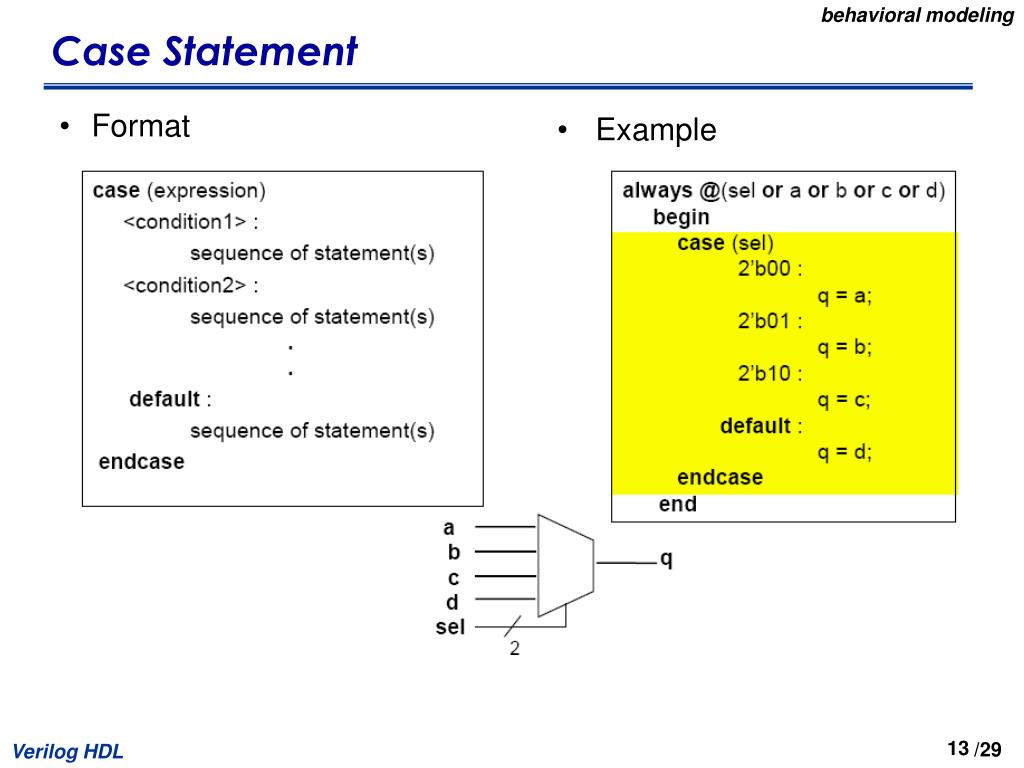

Case Statement Examples In Verilog Web A single bit multiplexer will have one control line two inputs say X and Y and one output say Z When the control is 0 X is connected to Z When the Control is 1 Y is connected to Z The figure below explains this Let

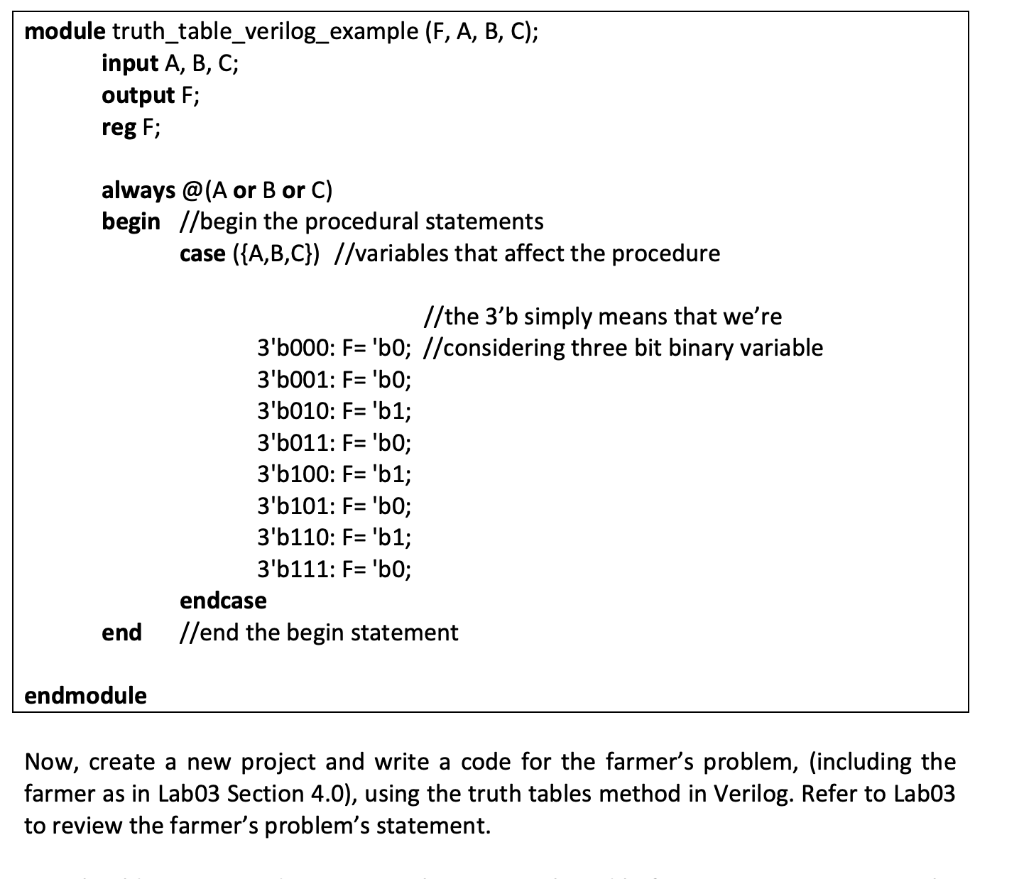

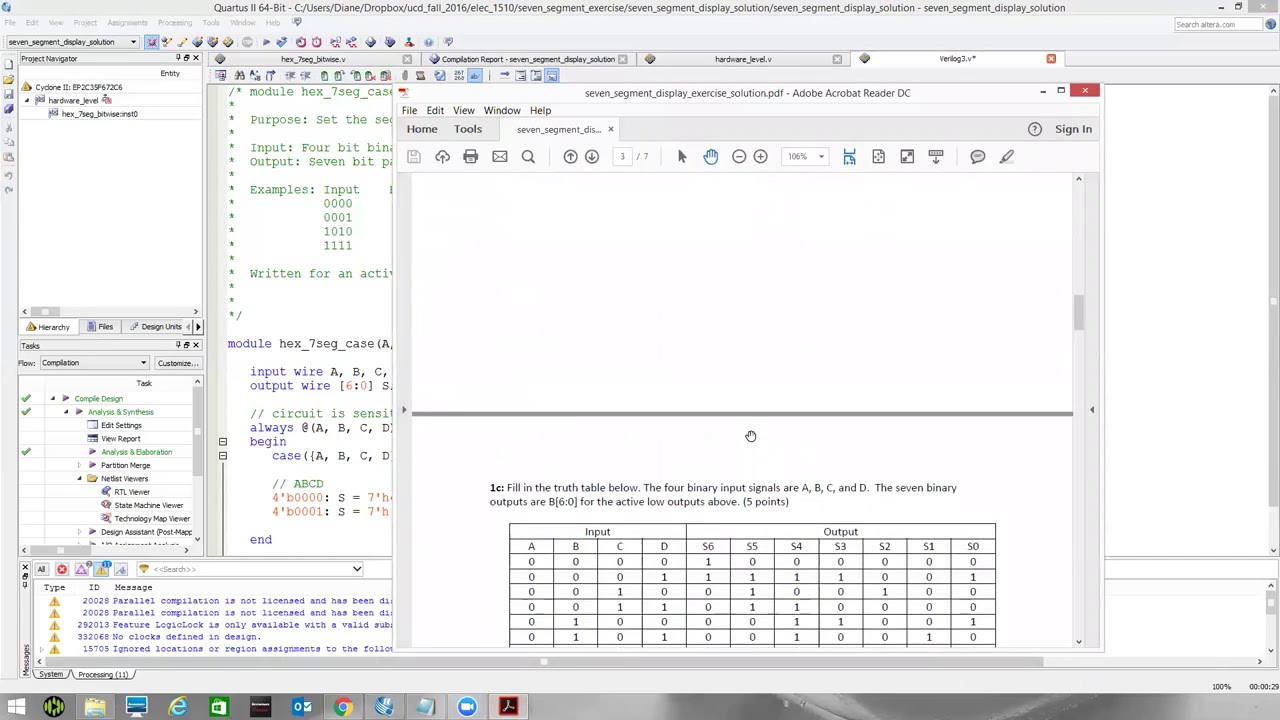

Web Jan 31 2019 nbsp 0183 32 Example 1 Use the Verilog if statement to describe a 4 to 2 priority encoder with the truth table below The following code is a Verilog description for this priority encoder Web Oct 11 2020 nbsp 0183 32 The case make and the if announcement are and examples of sequential statements inside verilog In the rest of this post we talk about how both of these statements are use in verilog We then examine a short example for both of these constructs to show how we use them in train Verilog If Statement

Case Statement Examples In Verilog

Case Statement Examples In Verilog

Case Statement Examples In Verilog

https://i.ytimg.com/vi/rY5fsNUUt5k/maxresdefault.jpg

Web 1 day ago nbsp 0183 32 Case Statements A case statement tests and expression and then enumerates what actions should be taken for the various values that expression can take For example case sel 0 out in0 1 out in1 2 out in2 3 out in3 endcase

Templates are pre-designed documents or files that can be used for different purposes. They can save time and effort by providing a ready-made format and design for creating different sort of content. Templates can be utilized for individual or expert tasks, such as resumes, invites, leaflets, newsletters, reports, discussions, and more.

Case Statement Examples In Verilog

VerilogVHDL Interview Question Difference Between If else If elseif

PPT Components Of A Verilog Module PowerPoint Presentation Free

HDL Verilog Online Lecture 25 For Loop Repeat Forever Loops

Casex Example

Tutorial 33 Verilog Code Of Serial In Parallel Out Shift Register

PDF Verilog HDL And Its Ancestors And Descendants

https://fpgatutorial.com/verilog-if-statement-case-statement

Web Oct 11 2020 nbsp 0183 32 The case statement and the if statement are both examples of sequential statements in verilog In the rest of this post we talk about how both of these statements are used in verilog We then consider a short example for both of these constructs to show how we use them in practise

https://vlsiverify.com/verilog/case-statement

Web The case statement also has a total of three variations case casex and casez Note the following differences case considers x and z as it is as shown in above example If an exact match is not found the default statement will be executed casex considers all x and z values as don t care casez considers all z values as don t cares

https://stackoverflow.com/questions/21401557

Web Jan 29 2014 nbsp 0183 32 Let me explain with an example Mux If there were only 2 select lines always A 1 0 begin case A 1 0 2 b00 select 4 b1110 2 b01 select 4 b1101 2 b10 select 4 b1011 2 b11 select 4 b0111 endcase end For 3 select lines

https://www.verilogpro.com/verilog-case-casez-casex

Web Sep 13 2015 nbsp 0183 32 The Verilog case statement is a convenient structure to code various logic like decoders encoders onehot state machines Verilog defines three versions of the case statement case casez casex Not only is it easy to confuse them but there are subtleties between them that can trip up even experienced coders

https://verilogams.com/refman/modules/analog-procedural/conditional.html

Web 3 days ago nbsp 0183 32 A case statement tests and expression and then enumerates what actions should be taken for the various values that expression can take For example case sel 0 out in0 1 out in1 2 out in2 3 out in3 endcase If the needed case is not found then no statements are executed

Web Aug 16 2023 nbsp 0183 32 Case Statement in Verilog Like C C or any other programming languages Verilog has case keywords which we can use to describe a hardware or use it in verifying the hardware First we ll see how to use this Web Aug 19 2021 nbsp 0183 32 1 You don t seem to be showing us all of your Verilog code that makes it tough to help you However I see that you have the clk and in signals changing at the same time which can cause unpredictable behavior Change the transitions of your inputs to be 2 or 3 nanoseconds before the rising clock edge

Web A case statement is used to assign the correct input to output supported the value of sel Since sel can be a 2 bit signal it ll have twenty 2 combos zero through 3 The default statement helps to line output to zero if sel is 3 module my mux input 2 0 a b c